들어가는 글

반도체는 동작 방식이나 사용 용도에 따라 여러 제품으로 분류할 수 있다. 메모리 반도체와 비메모리 반도체(시스템 반도체)로 구분을 시작하여 메모리 반도체 내에서 휘발성 메모리, 비휘발성 메모리로 분류되고 더 많은 제품군으로 뻗어나간다. 이번 포스팅에서는 메모리 반도체의 대표주자인 D램과 낸드플래시에 관해 알아보도록 하겠다. D램은 휘발성 메모리, 낸드플래시는 비휘발성 메모리에 해당한다.

D램

D램, DRAM은 Dynamic Random Access Memory의 약자로서 동적 메모리를 의미한다. 여기서 '동적'이란 실행 중에 필요한 용량만큼 '유동적'으로 정보를 저장할 수 있다는 의미를 가진다. 실제로 D램은 물리적인 관점에서 정보를 저장하거나 지우기 쉽다. D램은 휘발성 메모리로서 전원이 꺼지면 저장된 데이터를 모두 잃게 된다. 전원이 켜져 있더라도 중간중간 전자가 소실되어 정보가 사라지기 때문에, 주기적으로 전자를 다시 채워서 정보를 잃지 않도록 하는 refresh 동작이 필요하다.

D램 기본 동작 원리

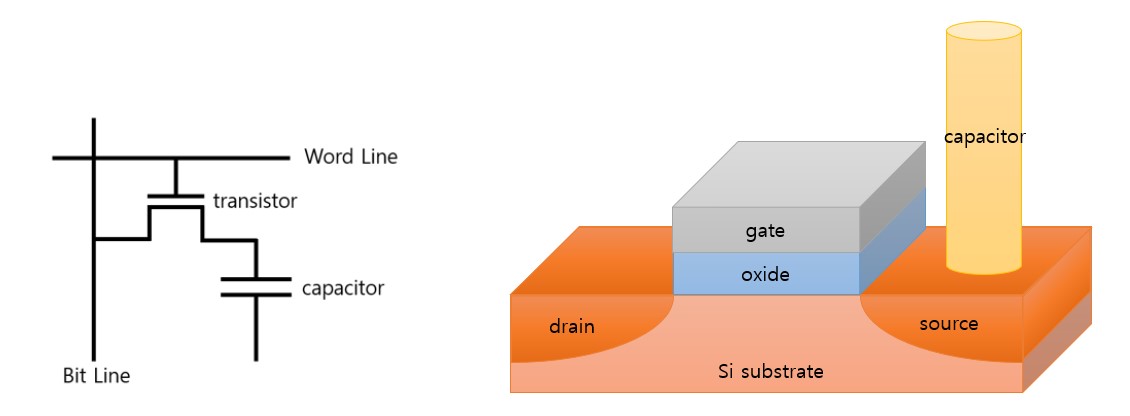

D램은 cell이라는 기본 단위로 이루어지고, 하나의 cell은 하나의 트랜지스터와 하나의 커패시터의 조합으로 구성된다. 커패시터 속에 전자가 존재하는지 여부에 따라 '0' 또는 '1'로 구분해 2진법으로 데이터를 저장한다. 아래 그림이 D램 기본 구조 (unit cell)를 회로도와 3D 구조로 표현한 그림이다. 트랜지스터의 source 쪽에 커패시터가 만들어지고 트랜지스터의 gate 쪽을 word line이, drain 쪽을 bit line이 제어하도록 배선이 형성된다. 데이터가 저장되는 과정을 간단하게 살펴보면, word line에 전기적 신호가 흐르면 트랜지스터가 동작 가능한 상태가 되고, 이때 bit line에 전기적 신호가 흐르면 트랜지스터를 통해 전자가 커패시터로 이동하여 정보 '1'이 저장된다. 정보를 저장하고 읽고 지우는 동작에 관해서는 추후 다른 포스팅을 통해 알아보도록 하겠다.

낸드플래시

낸드플래시, NAND Flash는 플래시 메모리의 일종으로, NAND 논리연산자 방식을 사용하는 플래시 메모리이다. 우선 플래시 메모리라는 이름은, 큰 단위로 정보를 한 번에 지울 수 있기 때문에 카메라 플래시와 비슷하다고 하여 붙여졌다. 플래시 메모리는 비휘발성 메모리로서 전원이 꺼져도 데이터를 잃지 않고 보존할 수 있다. 플래시 메모리는 사용하는 논리연산자 방식에 따라 NAND 타입과 NOR 타입으로 나뉘는데, NOR 타입은 cell이 병렬로 배열되어 있어 집적에 어려움이 있는 반면, NAND 타입은 cell이 직렬로 배열되어 있어 집적에 용이하기 때문에 용량을 늘리기 쉽다는 특징이 있다. 따라서 양산용으로는 대용량 저장장치를 만들 수 있는 NAND 타입의 플래시 메모리가 적합하다.

낸드플래시 기본 동작 원리

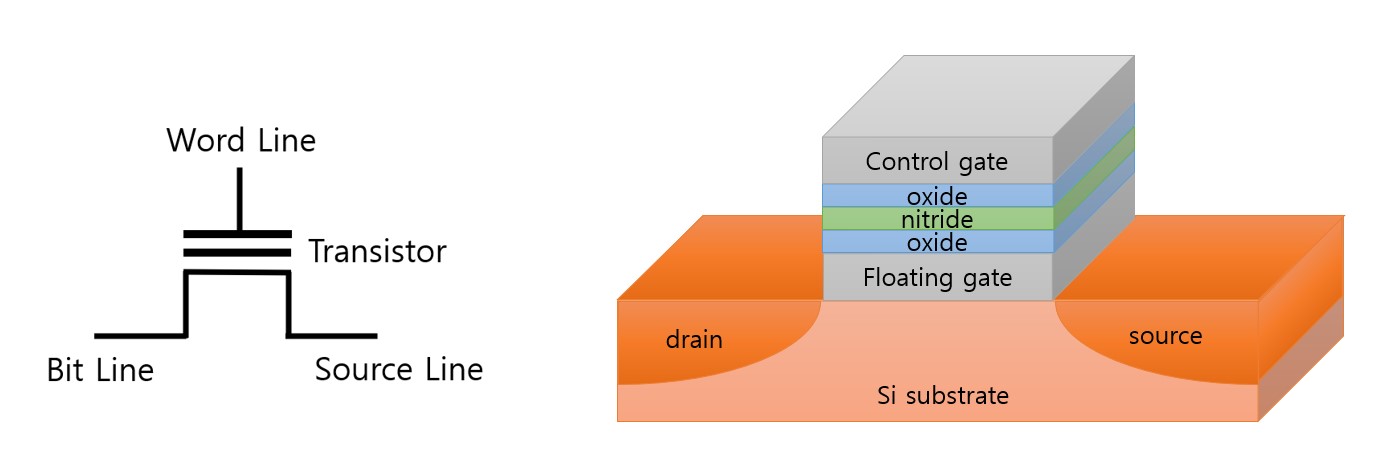

낸드플래시의 기본 단위(unit cell)는 특정 gate 구조를 가지고 있는 트랜지스터 하나이다. 일반적인 MOSFET 구조에서 O에 해당하는 oxide단이 oxide-nitride-oxide 삼중구조인 ONO로 구성된다는 특징이 있다. 가장 상단에 있는 control gate에 word line이 연결되고, drain 쪽에 bit line이 연결된다. word line을 통해 gate에 전압을 인가하고, bit line을 통해 drain에 threshold voltage 이상의 전압을 인가하면, drain과 source 사이에 채널이 형성되고 drain에 있던 전자가 채널을 통해 source부로 이동하게 된다. 이때, 전자가 drain에서 출발하여 channel을 지날 때, floating gate에 trap(잡히게)된다. 그러한 과정을 통해 floating gate에 전자를 저장하는 것을 program이라고 하며, 정보 '0'에 대응된다. (여기서 threshold voltage는 floating gate에 저장된 전자량에 따라 달라진다.) 한편, Si substrate의 body 영역에 전압을 인가하면 floating gate에 저장된 전자가 Si substrate 쪽으로 이동하게 된다. 그렇게 floating gate에 있던 전자를 빼내는 동작을 erase라고 하며, 정보 '1'에 대응된다. floating gate에 전자를 trap 시키고 빼내는 것이 핵심 동작 원리이기 때문에 의도치 않게 전자가 소실되지 않도록 oxide 층을 ONO 삼중구조로 구성했다는 것을 자연스레 이해할 수 있을 것이다.

'반도체 > 반도체 지식' 카테고리의 다른 글

| isolation 공정: LOCOS (LOCal Oxidation of Silicon) (0) | 2023.07.06 |

|---|---|

| sheet resistance(면저항)과 4-point probe 장비 (0) | 2023.07.06 |

| Si의 결정구조 (단결정, 다결정, 비정질) (0) | 2023.02.20 |

| 반도체 8대 공정 개요 3 - 증착/이온주입 (0) | 2023.01.24 |

| 반도체 8대 공정 개요 2 - 포토/에치 (0) | 2023.01.23 |